Thanks to Moore's Law, automotive electrical systems have experienced rapid technological growth. Modern cars have grown considerably and are no longer simple motor electrical systems coupled with AM radios. Today's modern vehicles are equipped with advanced electronic systems that perform engine control, advanced driver assistance (ADAS), traction and stability control, infotainment and more, while also providing autonomous operation for some cutting-edge applications.

The significant growth in the deployment of such in-vehicle electronic systems has also brought several challenges that must be addressed by designers:

• Performance – Real-time, low latency and highly deterministic performance is required to implement a variety of in-vehicle functions such as ADAS, ECU, traction and stability control.

· Safety – Automotive electronic systems perform critical functions that can cause injury or death. Therefore, the system must implement information security and tamper-proof technology to prevent unauthorized modifications.

· Safety – must meet the automotive safety integrity level specified in ISO26262.

• Interface – must be able to connect a variety of sensors, drives and other brakes.

· Power efficiency – must operate efficiently within a limited power budget.

· Software Definition – Flexibility to adapt to different standards and conditions in multiple markets.

To address these challenges, automotive electronics system developers are deploying on-chip heterogeneous system (SoC) devices. Heterogeneous devices combine a processing unit (usually a multicore) with one or more heterogeneous coprocessors (such as GPUs, DSPs, or programmable logic).

Combining processing units with programmable logic forms a tightly integrated system that takes advantage of the inherent parallelism of programmable logic. This feature enables the use of programmable logic (PL) for high-performance algorithms and interface connectivity, while the processing system enables more advanced decision making, communication, and system management functions. Once combined, the programmable logic can be shared with processing tasks to create a more responsive, deterministic, and energy-efficient solution.

For interface connectivity, heterogeneous SoCs support a variety of industry-standard interfaces that can be implemented through processing systems or programmable logic. Thanks to the flexibility of the IO structure, programmable logic can be used to implement key legacy and custom interfaces. However, this requires adding an external PHY to implement the physical layer of the protocol, providing any connectivity.

Some heterogeneous SoCs support multiple device-level and system-level security features for easy implementation. These devices encrypt and verify the boot and configuration process. If the processor core is based on an ARM processor, Trustzone can be used to secure the software environment. With Trustzone, development teams can create orthogonal environments that use software to limit software access to the underlying hardware. In addition, several additional design options are available here, such as functional isolation, which can be implemented in the design to further enhance the security solution depending on the requirements.

The traditional heterogeneous SoC development process divides the design into two parts: the processor system and the programmable logic. This approach used to require two separate development teams in the past, which increased non-recurring engineering costs, development time, and technical risk. In addition, the method also fixes the design functions in the processor core or programmable logic, making post-optimization difficult.

The development tools people need should be able to implement software-defined development of the entire device and have the ability to move functions from the processor core to the programmable logic as needed, and can be done by non-HDL experts.

This is where the system optimization compiler comes in handy. The System Optimizer compiler can define the entire system behavior in software using high-level languages ​​such as C, C++, or OpenCLTM. The system optimization compiler is then used to perform functional partitioning prior to the processor system and programmable logic that enables the functionality to move seamlessly so that the selection is to be implemented in the processor system or in programmable logic.

Figure 1 - Use the System Optimization compiler to select the features you want to speed up.

By using a built-in timer inside the processing system to time the function, you can find the bottleneck function and create a list of bottlenecks. These bottlenecks are candidates for acceleration in programmable logic by using a system-optimized compiler.

The movement between the processing system and the programmable logic is achieved through a combination of a high-level synthesis of the system-optimized compiler (a tool that converts C, C++, OpenCL programs into Verilog or VHDL descriptions) and a software-defined connection framework. . The software-defined connection framework seamlessly connects HLS results to software applications, which the design team uses to move functionality between the processor and programmable logic with one click. Of course, when users move functions to programmable logic, they also get a noticeable performance boost, which is naturally the result of using programmable logic. Acceleration in the PL improves determinism and reduces latency compared to CPU/GPU solutions, which is critical for applications such as ECUs and ADAS.

Figure 2 - Estimating resources and performance using the System Optimization compiler.

Library support

Many automotive applications are developed using industry standard open source libraries, such as OpenCV or Caffe in ADAS systems, or standard math libraries in ECUs. To speed the development of these applications, the system optimization compiler needs to be able to support multiple HLS libraries for developers to use in their applications. The system optimization compiler should support multiple key libraries, including:

· OpenCV – accelerates computer vision

· Caffe – accelerates machine learning inference engine

· Math Library – provides a synthesizable implementation of standard math libraries.

· IP Library – Provides an IP library for implementing FFT, FIR, and shift register LUT functions.

· Linear Algebra Library – provides a library of general linear algebra functions.

· Arbitrary precision data type library – Supports non-zero power arbitrary length data using signed and unsigned integers. This library allows developers to use FPGA resources more efficiently.

The provision of these libraries provides considerable support to the development team, eliminating the need for development teams to develop similar functionality.

Real instance

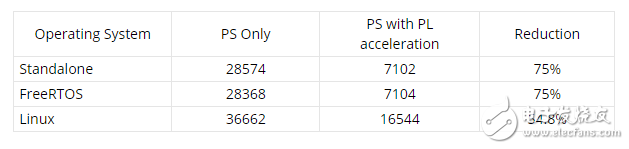

A key element of many automotive applications is protecting data to prevent unauthorized modifications and avoiding unsafe operations. A common algorithm used to secure stored data and transmitted data is the Advanced Encryption Standard (AES). AES is described at a high level, but is best suited to an example of an algorithm implemented in a programmable logic architecture. To demonstrate the benefits of using a system-optimized compiler, a simple AES 256 application for three common operating systems has been developed. The instance was initially executed only in the processor system and then accelerated in the programmable logic.

Figure 3 - AES acceleration results for different operating systems when using the system optimization compiler.

in conclusion

Heterogeneous SoCs address the challenges faced by automotive electronics system designers. By using a high-level language, the system optimization compiler can develop these devices. Once the processor is used to develop and prototype the application functions, the functional partition between the processor system and the programmable logic can be optimized to shorten Develop time to achieve a safer, more responsive, and more energy efficient solution.

Do you know which is the most competitive student laptop for elementary students or daily entertainment? It`s this 14.1 inch celeron n4020 64gb laptops on sale for students, since not only lightweight, but also entry celeron cpu, storage, longer lasting battery, etc. More than 80% clients choose this student chromebooks for students tender cause it`s of all features of laptop for online classes. Of course, this model is also suitable for operating student laptop deals.

As a professional oem&ODM manufacture, never let you down. No matter you look for 14inch 64gb student pc, 15.6 inch N5095 Teacher Laptop, 15.6 inch 10th or 11th University Laptop, 16.1 inch 4gb graphics recommended laptop for programming, Android Tablet, Mini PC or All In One PC , always have the right one here for you.

Therefore, just feel free to contact us and share your basic requirement, like size, cpu, ram, rm, quantity, special requirements, so that send back right details for you.

Student Laptop,Student Laptop Deals,Laptops On Sale For Students,Student Pc,Laptop For Online Classes

Henan Shuyi Electronics Co., Ltd. , https://www.shuyielectronics.com