According to a survey by IMS Research, the number of car audio consoles with video capabilities will increase from 8.5 million units in 2006 to 26.6 million units in 2015. In order to provide information to the driver without distracting it, the display needs to be mounted away from the car audio unit and projected onto the back of the windshield. This video interface, which combines image sources and panels, is increasingly moving from analog video technology to higher quality RGB (red, green, and blue) digital video formats, which have become standard interfaces used in LCD displays. The cable length of the front-end display application is typically maintained in the range of 1 to 3 meters, while the cable for the rear seat entertainment (RSE) unit needs to be 8 meters or more. This connection supports gigabits per second of data transfer rate, far exceeding the baud rate of traditional in-vehicle networks, and is perfectly implemented with a point-to-point serializer/deserializer (SerDes) solution. This chipset greatly reduces the number of pins in the transmission line and connector compared to the wider parallel video bus, resulting in superior system-level advantages.

This article refers to the address: http://

To meet the stringent requirements of automotive display interfaces, such as high data throughput, ultra-thin wiring, advanced signal conditioning, detectability, and ultra-low EMI (electromagnetic interference). National Semiconductor (NS) has developed the DS90UR905/6 and DS90UR907/8 SerDes chipsets, which are XGA (1024 x 768) embedded that can extend resolution from QVGA (400 x 240) to 24-bit color depth. Clock SerDes solution. A wide range of pixel clock frequencies allows automakers to use a digital video display interface solution across their entire vehicle range to cover from dual-panel small dashboard panels, center console LCDs to larger RSE displays application.

Video application and SerDes concept

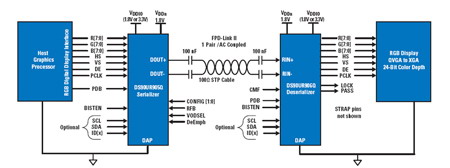

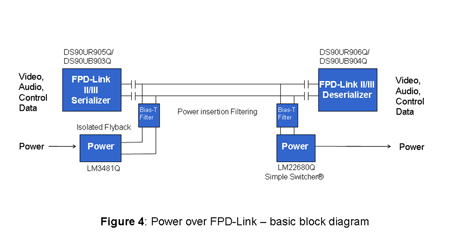

The target application area for the SerDes component is the flat panel display link interface, which connects the image host to the display via a long serial cable. Typical examples include a central information display (CID), a dashboard, an entertainment display on a headrest, or a roof-down display module for a rear seat passenger, as shown in FIG. These new chipsets are part of NS's "FPD-Link II" family of products that convert 27-bit digital RGB color information and time control signals from a video source into a single serial data embedded with clock information. The stream is transmitted over the twisted pair. The chipset uses a high-speed differential signal at the I/O (input/output) layer, that is, the actual signal is transmitted on the "true" (positive) terminal, and the "complementary" (negative) terminal transmits the corresponding signal. The opposite polarity signal.

Figure 2 depicts the concept of video transmission at the system level. In addition to color and timing bits, there is an optional I2C control interface that replaces the component configuration through the regular pin-band options. The chipset supports 18bpp (bits per pixel) or a color depth of 24bpp. The color display uses 3 sub-pixels (red, green, blue) to define a single pixel. Since each pixel has 18 bits (6 bits of red, 6 bits of green and 6 bits of blue), we can get 262,000 colors. Most people can see more than 10 million colors in their eyes, which explains why using 24bpp has become a trend: it offers more than 16 million colors for a richer user experience and a smoother color gradient. The pixel clock range is now extremely wide: the frequency can range from 5MHz to 65MHz, which increases the serial link rate from 140Mbps to 1.82Gbps, covering all mainstream resolutions of automotive displays.

Parallel LVCMOS input and output signals can be flexibly aligned to the sync transmitter input and the receiver's recovered output clock (PCLK) rising or falling edge, respectively, which greatly simplifies the serializer to image controller and deserializer to Interface connection of the LCD timing controller. The SerDes chipset does not require an external reference clock (quartz or oscillator) in the "pre-synchronized" receiver PLL in a certain frequency band around the transmitter's parallel clock. This synchronization is guaranteed even during all possible random data mode transfers, which is known as the "random data lock" feature. This not only saves the cost of the reference component system, but also eliminates another potential source of electromagnetic interference. This performance can also be "hot swapped", which means that assertion/deassertion operations can be performed on the serial data stream destined for the deserializer without any special sequencing or training modes.

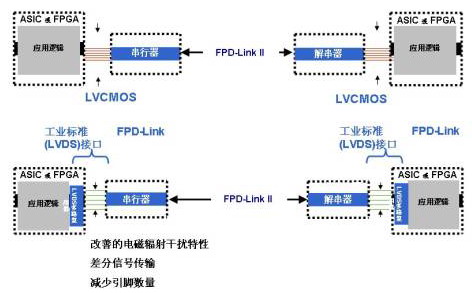

Once the receiver PLL is locked at the transmitter frequency, this state is displayed by the LOCK output flag pin, ensuring the data integrity of the receiver output. The DS90UR907/8 chipset has all the features of the DS90UR905/6 chipset. The difference between the two ears is that the input and output are no longer parallel buses that transmit LVCMOS signals, but follow the open industry standard "FPD-Link". Many modern image controllers, display timing controllers, ASICs, and FPGAs support this "primary serialization" technology, which uses three data channels for 18bpp or four data channels for 24bpp, each There is a parallel clock channel. The transmission of electrical signals follows the open ANSI/TIA/EIA-644A standard, which is also known as "LVDS" (Low Voltage Differential Signaling). The advantage of using this interface technology instead of conventional LVCMOS is that the use of differential signals reduces electromagnetic interference and reduces the number of pins in the component, as shown in Figure 3.

Figure 3 Advantages of the FPD-Link system interface options

FPD-Link II payload

In each pixel clock cycle, 28 "sub-symbols" are time-division multiplexed on the differential I/O to be converted into a serial data stream. The embedded payload contains 24 color bits, 3 timing signals (horizontal sync-HS, vertical sync-VS, and data enable-DE) and additional bits. The interconnect rate is 28x pixel clock. At 65 MHz, this rate translates to 1.82 Gbps. The serial data stream is defined by the "CLK1" HIGH bit of the front end and the "CLK0" LOW bit at the end, thereby achieving a smooth transition between high and low levels between each frame, allowing the serializer's PLL to synchronize with it. And extract embedded clock information. Two additional bits ("DCA" and "DCB" bits) are placed in the middle of each frame and include timing signals embedded in the DCA and DCB bit transitions. In order to reduce harmonic electromagnetic interference and improve signal quality, the payload bits are randomized, balanced, and scrambled, while establishing DC balance for AC coupling.

The longer the cable connection, the more likely the ground potential drift between the transmitter and receiver modules, and the AC-coupled interface scheme can achieve potential decoupling by using series capacitors in the transmission line. The DC balanced encoder in the serializer and the DC balanced decoder in the corresponding deserializer achieve uniform distribution between high and low bits on the serial link to prevent ISI (intersymbol interference) effects and capacitance The blocking of the static mode. By arranging the capacitors at both ends, the solution also provides input/output short-circuit protection in the event of cable damage or short-circuit to the ground or board net voltage. Randomization and irregularity not only ensure good eye opening, but also minimize electromagnetic interference on interconnected lines. Overall, the coding efficiency is higher than 85%.

Enhanced signal conditioning

Signal conditioning technology plays a crucial role in driving long-distance high-speed connections, using signal reduction features on the serializer side. Figure 4 is an example of a signal restoration operation. The series of converted bit streams are 0, 1, 000, and 1, in turn, with a single-ended (SE) waveform at the top of the graph that can be measured at true and output terminals relative to ground. A differential (DIFF) signal is given at the bottom of the graph, which is equivalent to the differential voltage swing at the receiver input in its terminal range. For the first conversion, the first signal sent is 0, forming a fully differential swing. The next conversion is a 1, which is also a full voltage swing. Next in the C, D, and E time frames is a series of zeros, where the first 0 is the full voltage swing. With the arrival of the second and third zeros in time slots D and E, the amplitude will drop, indicating that the signal is "recovered". Therefore the static charge in the cable will be limited, otherwise it will increase over time. This causes the last bit 1 transmitted in time slot F to form a fully differential swing. The signal reduction characteristic is usually the internal energy that balances the high and low frequency signals in the transmission line. The overall effect is a clear signal eye opening, which is followed by a single bit transition after a long sequence of 1 or 0. The signal reduction layer is programmable to adjust to the optimal compensation level for a particular cable medium.

In addition, the signal reduction feature has a good effect on the adjustable differential output voltage (Vod), which doubles the differential output voltage (Vod) of long cable transmissions. Signal recovery does not require a significant reduction in the signal amplitude of the receiver input for signal recovery. A cable equalizer is integrated at the input of the deserializer. When regenerating all signal waveforms, this function is equivalent to a high-pass filter with respect to the input signal, which can partially eliminate the low-pass filter effect caused by the transmission medium. The equalizer is programmable between gains from 1.5dB to 12dB. Of course, all enhanced signal processing features can also be used in concert to establish sufficient eye opening for error-free data recovery in long cable runs.

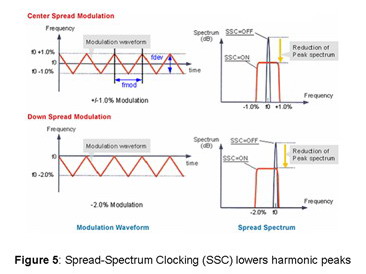

Spread spectrum clock

The deserializer is enhanced by an integrated configurable spread spectrum clock (SSC) generator. At the receiver output bus, this causes the output clock frequency and data spectrum to vary slightly over time with a low modulation rate of tens of KHz. As shown in Figure 5, the frequency change can occur near the nominal pixel clock center frequency ("central spread spectrum modulation"), or toward a lower frequency ("down-spread modulation"). The percentage of spectrum spread can be as high as ±2%. The spread spectrum clock spreads the peak energy over a wider spectrum, thus greatly reducing the electromagnetic interference noise level, rather than converting all outputs at a constant frequency at the same time point, where the radiated noise is concentrated in a narrow frequency band. All output data is synchronized with the output clock, which allows the data and clock to be effectively expanded. In particular, the DS90UR906 receiver output has a low voltage (LV) CMOS interface option that greatly reduces electromagnetic emissions.

Enhanced diagnostic capabilities

Another feature is the built-in self-test (BIST) feature. In this mode, the transmitter transmits a pseudo random code sequence (PRBS). The same sequence is generated internally by the receiver and compared to the received bit pattern. In order to find the best compromise between the overall test time and the lowest bit error rate that needs to be verified, the user can control the duration of the BIST. The PASS pin switches clockwise when a bit error payload is encountered. The PASS pin stores the final result of the BERT (Bit Error Rate Test). If the test fails, one or more load errors have occurred; if the test passes, there is no error in the propagation and reception of the PRBS sequence. At the far end of the link, BIST does not require any data generators, data logging or measurement systems. Automotive manufacturers can use the BIST mode to test the system and check the link operation. It can also be used as a test bed in the system development phase to send data to the entire link without a video source, while only applying a clock signal to the transmitter. During the service or troubleshooting phase, system tests can be used to verify that the link is working properly to lock the problem area on the host or display. Finally, when the car is started, the display interface can perform routine checks and verify connectivity.

More enhancements

Additional enhancements include integrated termination resistors that reduce board design complexity, resulting in lower cost and smaller board space. A terminal common mode filter pin is provided at the input of the deserializer. It is recommended that the user ground the common mode pin through the capacitor to ensure stability and ensure that the frequency is filtered out of the common mode voltage. This will reduce the level of electromagnetic radiation to the outside world and at the same time increase the resistance to external noise sources. The resistance of the digital video link to external interference is usually studied by a high current injection (BCI) test, which uses an inductor to modulate the side current of up to 300 mA onto the cable shield. The I/O library is powered by VDDIO, either 1.8V or 3.3V. This flexibility can take advantage of low interface levels and provide compatibility with downstream devices.

In general, when operating components at 1.8V, the level of electromagnetic interference is also reduced. In the event of a power failure, the output voltage state of the deserializer can be set to three-state (high-impedance) or low-resistance. The pixel clock (PCLK) state can also be set to three-state or low-impedance to select to stop the internal oscillator. In the latter case, the clock output will always exist regardless of the input signal. When the interface is only connected to a short-distance light-load bus, the Receiver Drive Strength (RDS) feature minimizes the current consumption of the output bus, slows the output edge slew rate, and ultimately reduces electromagnetic interference. The chipset supports an extended temperature range of -40°C to +105°C, making it suitable for a wide range of automotive electronic systems in a variety of operating environments. These chipsets are packaged in LLP and take up very little space and are certified for full automotive applications with RoHS and AEC-Q100 Grade 2 standards.

Summary of this article

The new DS90UR905/6 and DS90UR907/8 FPD-Link II chipsets offer many system advantages and enhancements. The parallel video bus is serialized into a single group with an embedded clock, which reduces system cost, eliminates clock/data skew issues, reduces noise, and extends the link to long-distance cable distances. The chipset supports all common automotive LCD resolutions from QWVGA to 24-bit color depth XGA. To facilitate system design, certification, and approval, designers can focus more on how to reduce EMI characteristics. This minimizes the cost of protection requirements without sacrificing reliability. Diagnosing the BIST mode is beneficial for factory testing and practical applications, as well as for troubleshooting testing and diagnostics. As the third-generation chipset in the FPD-Link II family of products, its components are based on proven and trusted IP protocols and are backward compatible with previous generations of chipsets. The FPD-Link II chipset family represents an optimized and automotive-ready solution for the automotive industry because it combines with low-density circuitry without compromising performance, high bandwidth, low power consumption, low EMI, and ruggedness. Autonomous link synchronization can be achieved.

JIANGYANG Special Cables are shipboard wire, diesel engine dedicated cable, sensor dedicated cable, profibus cable, solid PE insulated radio frequency cable with solid PE dielectric, coaxial cable with physical-foamed polyethylene insulation used in CATV systems, RG Serials polyethylene insulation coaxial cable, muticore and symmetrical pair/quad cable for digital communications horizontal floor wiring-solid polyethylene insulate.

Wire Cable,Special Cable,Tinned Copper Wire,Flame Retardant Shipboard Flexible Wire

Jiangsu Jiangyang Special Cable Co,.Ltd. , http://www.jymarinecable.com