**1. Introduction**

Image information is one of the most intuitive forms of data in human perception, playing a crucial role in helping us understand the world. With the rapid development of microelectronics technology, image information has evolved significantly—from analog to digital, from black and white to color, and from visible light to multi-spectral imaging. As a result, image quality—such as resolution, clarity, and detail—has improved dramatically. However, human demands for image quality continue to rise. Among all types of images, visible light images are most similar to what the human eye perceives, making their quality even more critical. Unfortunately, due to limitations in visible light transmission and imaging mechanisms, images often suffer from issues like fog, low light, and poor contrast. These problems cannot be fully resolved during the imaging process and require post-processing. Additionally, in applications such as image tracking, the time delay caused by image processing can severely limit the performance of servo systems. To address these challenges, this paper presents a real-time image dehazing enhancement system based on TI TMS320C6455 DSP and FPGA, which has been successfully applied in engineering practice.

**2. System Structure and Working Principle**

**2.1 System Architecture**

The image dehazing enhancement system is built using a DSP+FPGA architecture. The DSP used is the TI TMS320C6455, a high-speed fixed-point digital signal processor developed on TI's third-generation C6000 platform, operating at 1.2 GHz. It features 256 kbit of L1P program cache, 256 kbit of L1D data cache, 16 Mbit of L2 cache, a 64-bit EDMA controller, and an EMIF interface that supports widths of 16-bit, 32-bit, and 64-bit with a maximum speed of 100 MHz. The FPGA employed is the Altera Stratix II EP2S60-F1020C5, which includes 60,440 logic units, 318,024 kbit of total RAM, 36 DSP blocks, 144 18x18 multipliers, 12 PLLs, and up to 718 I/O pins. For video encoding and decoding, the system uses the DS90CR285 and DS90CR286 chips from Texas Instruments.

**2.2 Working Principle of the System**

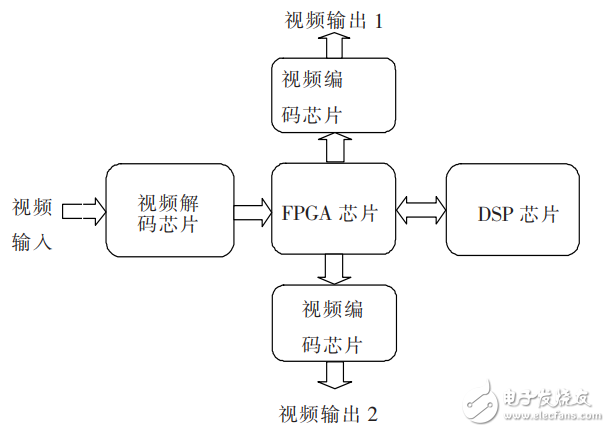

The block diagram of the system is shown in Figure 1.

**Figure 1: Hardware block diagram of the real-time image dehazing enhancement system**

The DSP+FPGA-based image processing system is a mature and widely used hardware structure known for its stability and efficiency. In this architecture, the FPGA typically acts as a scheduler, while the DSP handles the main image processing tasks. In applications like tracking, image data usually flows in one direction into the DSP, and processed results are output afterward. For real-time video processing, large volumes of image data can be input via the EMIF interface, and outputs can be generated in real time. However, during dehazing and enhancement, the system must not only process the input image but also avoid blocking the EMIF port by handling input and output separately. This requires temporary storage of image data, introducing some delay. To eliminate this delay, the proposed system delegates parameter determination to the DSP while implementing the dehazing algorithm entirely in the FPGA. This approach reduces the data transfer delay between the DSP and FPGA, and since the FPGA operates purely in hardware, it achieves better real-time performance.

Modified Sine Power Inverter,Sine Wave Vs Square Wave Inverter,Modified Sine Wave Power Inverter,Modified Sine Wave Inverter

zhejiang ttn electric co.,ltd , https://www.ttnpower.com