This paper proposes a high-resolution graphics image compression scheme based on FH8735 video and audio encoder, which can complete video capture and compression, and send the compressed video data to the host storage through the PCI bus, or output through the Ethernet interface. Realize remote real-time monitoring.

1 overall design

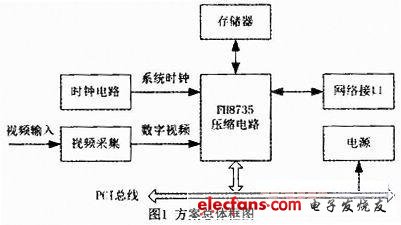

The high-resolution graphics image compression scheme based on FH8735 video and audio encoder consists of acquisition circuit, clock circuit, FH8735 compression circuit, network interface and power supply circuit. The overall block diagram of the program is shown in Figure 1.

The circuit of each part in Figure 1 is introduced as follows:

(1) Video capture circuit. Completing high-resolution video acquisition by input matching and video acquisition circuits;

(2) Clock circuit. Consisting of a high-performance crystal oscillator, it provides a stable clock for the video acquisition circuit and the FH8735.

(3) FH8735 compression circuit. It consists of FH8735 audio and video encoder and DDR memory, completes video compression processing, and provides PCI interface and network interface control.

(4) Network interface. An external PHY chip that provides an Ethernet interface;

(5) Power circuit. Provide the required power for each functional circuit.

2 main design

2.1 video acquisition circuit

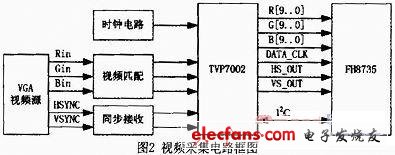

The video acquisition circuit is composed of TI's video image decoder TVP7002. The TVP7002 is a high-performance video image decoder with the following main functions and performance features:

(1) DC accuracy: 8/10 bits;

(2) Analog gain range: -6 ~ 6dB;

(3) Input component video signal resolution: 480i/576i~1080p;

(4) Input graphics signal resolution: VGA ~ UXGA;

(5) Digital video output format: YCbCr 4:2:2 and RGB/YCbCr 4:4:4;

(6) I2C bus interface.

The video acquisition circuit design with video image decoder TVP7002 as the core is shown in Figure 2:

After VGA video input, the signal can be matched and filtered to access the TVP7002 decoder. The operating state of the TVP7002 decoder is set by the FH8735 video and audio encoder through the I2C bus according to signal characteristics and processing requirements.

2.2 FH8735 video compression

FH8735 is a high-performance audio and video coding chip developed by FX Microelectronics. Its main technical features are as follows:

(1) Coding standard: ITU-T rrcommendaTIon H.264 ISO/IEC 14496-10 advanced video coding standard (MPEG4 Part 10), supporting H.264 Main Profile and Baseline Profile;

(2) Support maximum resolution: 2048 & TImes; 1024;

(3) Support 1 channel 1080i HD/2 channel 720pi HD/8 channel D1 input;

(4) 8-channel I2S input interface; configurable as master mode and slave mode;

(5) PCI interface, 32bit, clock frequency 33/66MHz;

(6) 2 independent DDR SDRAM controllers, each controller has a word width of 32 bits;

(7) One MII/RMII interface supports 100/10Mbps speeds and is fully compatible with the IEEE802.3 specification;

(8) One channel video output interface, in line with BT.656 video standard;

(9) 2 independent I2C interfaces;

(10) JTAG download debugging interface;

(11) 16 bidirectional GPIOs.

The FH8735 supports H.264 Main profile and Baseline profile video compression formats. It can perform 8-way clear 480i/576i real-time encoding, and can also encode real-time encoding of one 1080i and two 720p HD signals. In addition to high-performance video encoding capabilities, the FH8735 provides a rich video pre-processing feature for deinterlace, de-noise, OSD overlay, zoom, motion detection, etc. In order to configure an external video and audio receiver chip, the FH8735 provides two completely independent standard I2C interfaces to cope with possible external device I2C address conflicts. As a code coprocessor, the FH8735 is equipped with a flexible host interface. The host can communicate with the FH8735 via the PCI or HPI interface for control and status information, or access the FH8735 external DDR SDRAM. The FH8735 has two independent DDR controllers inside, which can be configured with one or two sets of external DDR SDRAM depending on the actual system requirements for encoder performance.

In order to meet the demand for preview video in some applications, the FH8735 has a standard set of BT.656 video output ports, which can split and merge the multi-channel preview video outputted by the video pre-processing unit as needed, and encode it into one BT.656 format. Video output.

stainless material,never be rusty.easy to install,just press the Diffuser Strip Light into the bracket until it is fixed well.Before installation,put the bracket on any place you want,then use the attached screw to fix. In ordet to fix the led srtips,three brackets per meter is enough.And you can rotate the bracket to make the shape ,of course the basic position should be confirmed before fixing the brackets.paticular design,make the strips different from other products,the brackets are only attached strip light,not sold separately.

Mounting Brackets,Led Mounting Brackets,Metal Mounting Brackets,Wall Mount Bracket

Guangdong Kamtat Lighting Technology Joint Stock Co., Ltd. , http://www.ip68ledstrip.com