1 Overview

The main goal of traditional embedded system design is to find an optimized architecture to complete a single, specific function. For such a system, the ASIC and core processor are considered as special building blocks: the designer chooses the appropriate ASIC according to the requirements of the application, based on the given performance requirements such as processor frequency, system stability, and Use appropriate processor cores for power requirements.

However, in today's mobile communication has entered everyone's life, today's embedded systems, such as PDA, has been different from the traditional embedded systems, they have their own unique characteristics. Objective requirements require that they can support multiple application functions such as web browsing, playing audio / video files, and wireless network communication.

In this way, the traditional design ideas cannot meet the needs of multi-application embedded systems because they only face a single application. A good way to solve this problem is to introduce programmable capabilities to the embedded system, so that the system can support different applications according to different requirements of users.

In order to introduce programmability into the system, we consider embedding FPGA in the system, because FPGA has the following characteristics, making it our first choice:

1. The processing power and logic capacity of the current FPGA are close to the dedicated ASIC, and the power consumption is relatively low, which can meet the requirements of our system design;

2. Due to the reprogrammability of FPGA, the embedded system using FPGA can meet various application requirements;

From the perspective of embedded system management, support for network communication is also necessary, and it is also a very characteristic application because it makes it possible to download new applications from remote servers and run them locally. In order to support this function, we use Java as the software platform. Because Java runs on the Java virtual machine, it can download and execute new application code, and there is no need to restart the system after downloading.

In summary, this new embedded system is based on Java and has an FPGA connected to a standard processor. We download Java code and bitstream that can program FPGA through the network. The system also supports dynamic reconfiguration of FPGAs. In order to realize the communication between the hardware (FPGA) and the software (Java application code), a set of local APIs are defined to enable the Java application layer to access the underlying hardware. In order to call these local APIs, the Java Native Interface (JNI) is used. In this article, some Java functions (Javamethod) are implemented with FPGA programmable hardware, which is called HW method.

2. System design

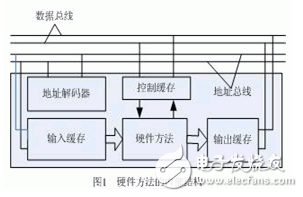

The logical structure diagram of the corresponding hardware method to realize a Java function is shown in Figure 1.

The input buffer and output buffer are used to receive input parameters and store output results, respectively. The control cache is used to control and detect the hardware method, such as issuing a startup instruction to the hardware method, checking its status, and judging whether the operation is completed. All caches in this module are mapped into the processor's physical address space, and the processor can use normal read and write instructions to complete access to these caches.

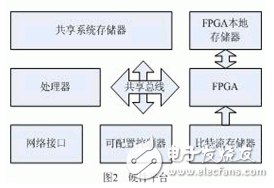

Figure 2 is the hardware platform of the embedded system, which consists of a standard processor, an FPGA and a system storage unit. They are connected together through a shared system bus.

When the processor issues a read and write operation instruction to a hardware method, the hardware method sends a corresponding response signal to the data bus with the help of its own address decoder. Here, we can think of the hardware / software communication commands initiated by the processor, and the FPGA responds as a slave unit. Because after the processor initiates the initial command, the configurable manager is responsible for managing the FPGA programming. In this way, the parallel operation of the processor and the FPGA is realized.

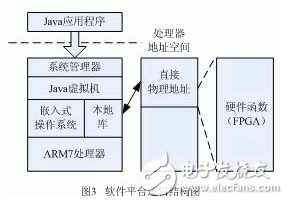

As shown in Figure 3, we chose Java as the software platform and loaded an embedded operating system to provide basic services for Java real-time applications, such as threading and other hardware management.

Through the system manager, you can download Java applications from a remote server. The system manager mainly implements the following three protocols:

1. Download protocol for application code (including bitstream that can program FPGA);

2. Protocols related to system maintenance for remote management;

3. An authentication protocol that controls access to embedded systems.

The system manager includes a client class loader based on socket connections. The remote application can be downloaded locally and executed according to the following procedure:

1. After completing the certification process, the system enters the management mode;

2. Download the application code to complete the system initialization, such as loading FPGA programmable bit stream to the corresponding storage unit;

3. Execute the new application.

In this system, in order to simplify, the hardware method address is mapped to the determined system physical storage area in advance, the purpose is for the convenience and quickness of the addressing operation.

Because we use the Java software platform, the application cannot directly access the underlying hardware. This means that applications running on the processor's Java virtual machine cannot directly access the cache area mapped to the hardware method in the FPGA. To solve this problem, in theory, the following two methods can be used:

1. Modify the Java virtual machine to have direct access to the processor's physical address;

2. A Java Native Interface (JNI) is designed separately so that applications can access the physical address to which the hardware method is mapped through the functions provided by the interface.

Although the first scheme is more efficient and does not introduce additional overhead, modifying the kernel of the Java virtual machine is quite tedious work and may also cause potential system instability. Although the second scheme introduces a certain extra cost, it is easy to transplant and implement. Therefore, we adopted scheme two, and designed a local communication library in addition to the Java virtual machine and the Java local interface.

The API form of the local communication library is as follows:

int hwWriteXXX (int addr, XXX p);

int hwWriteArrayXXX (int addr, XXX [] p);

XXX hwReadXXX (int addr);

XXX [] hwReadArrayXXX (int addr);

int hwConfig (int cf_mem_addr, int bitstr_size);

The form of the Java native interface layer interface is as follows:

class HWInterface {

staTIc int ConfigStatus;

public staTIc naTIve int setParam (CID hw_cid, object P)

{

if (type_of_P == XXX)

err = hwWriteXXX (hw_cid.addr, (XXX) P);

return err;

}

public staTIc native int getResult (CID hw_cid, object R);

public static native int setCMD (CID hw_cid, int cmd);

public static native int getStatus (CID hw_cid);

public synchronized static native int configHW (CID hw_cid);

}

In the above code, XXX represents basic Java data types such as integer, float, and double.

Java applications access local libraries through methods provided by the class HWInterface. The specific implementation of setParam is given in the code above. Among them, the CID is an object including the cache address to which the hardware method is mapped. The CID corresponding to each hardware method is unique. Therefore, the address and the size of the cache area have been determined in advance. However, because there is only one configuration controller in the system, we cannot program two or more hardware methods to the FPGA at the same time. It can also be said that only one hardware method can use the configuration controller at a time. To this end, a static variable ConfigStatus is introduced to reflect the current status of the configuration controller. Therefore, the function configHW () accessing the configuration controller is statically synchronized.

Using the interface given above, the following code

methodA ()

{

…;

int a = objA.m1 (2); // SW method

int b = objB.m2 (3); // HW method

int c = a + b;

…;

}

It should be written in the following form:

methodA ()

{

…;

1 HWInterface.configHW (cid2); // cid2 is the ID of HW method m2

2 Object P = new Integer (3);

3 HWInterface.SetParam (cid2, P);

4 HWInterface.startHW (cid2);

5 int a = objA.m1 (2);

6 Object R = new Integer ();

7 While (HWInterface.getResult (cid2, R) == 0)

; // wait until HW method finished

8 HWInterface.getResult (cid2, R);

9 int b = ((Integer) R.getValue ());

10 int c = a + b;

…;

}

In the above example, in order to execute the function objB.m2 () in the FPGA, the FPGA is first programmed (Line1). Then, copy the parameters to the input buffer of the hardware method (Line3), and initialize the hardware method (Line4). Finally, a loop function is used to continuously check the status of the hardware method cache (Line7, 8) until the calculation is completed, and then the result is copied (Line9).

3. System implementation

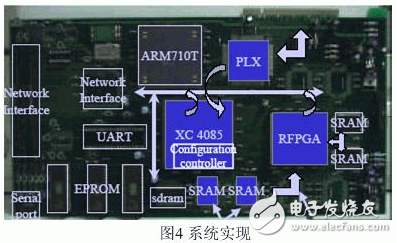

Using ARM710T processor and Virtex FPGA, according to the design scheme given above, we have implemented an embedded system development platform. The platform includes a network interface, two debug interfaces, a PCI host interface and a serial port. And transplanted an embedded operating system and a compact Java real-time operating environment. As shown in Figure 4:

4. Summary

This article uses a brand-new idea to improve the traditional embedded system and implements an embedded system platform that can support multiple applications. Taking advantage of the programmability of FPGA and the good portability of the Java platform, the platform can fully meet our design requirements. Of course, there are also deficiencies, such as obtaining the status of the configuration controller, you can consider using interrupts to achieve, rather than using the circular query mechanism in this article. This will be improved in future work.

High Speed Edge Sealing Machine

High Speed Edge Sealing Machine,Woven Bag Small Sealing Machine,Household Woven Bag Sealing Machine,Fully Automatic Woven Bag Sealing Machine

Dongguan Yuantong Technology Co., Ltd. , https://www.ytbagmachine.com